Готовы тестовые образцы процессоров EPI EPAC1.0

Европейская инициатива в области процессоров (EPI), проект с участием 28 партнеров из 10 стран, перед которым стоит цель добиться независимости ЕС в технологиях высокопроизводительных микросхем и инфраструктуре высокопроизводительных вычислений, сообщил, что отгружены первые образцы тестовых микросхем EPAC1.0. За этим обозначением скрывается процессор на архитектуре набора команд RISC-V, полностью спроектированный и изготовленный в Европе. Он состоит из IP-ядер ускорителей с высокой энергетической эффективностью и пропускной способностью под названием EPAC (European Processor Accelerators).

EPAC сочетает в себе несколько технологий ускорения, предназначенных для различных областей применения. В частности, тестовый процессор содержит четыре блока векторной обработки (VPU), состоящих из ядра Avispado RISC-V, разработанного SemiDynamics, и блока векторной обработки, разработанного Barcelona Supercomputing Center и Загребским университетом. Каждый блок также содержит Home Node и кэш L2, разработанные соответственно Chalmers и FORTH, которые обеспечивают согласованное представление подсистемы памяти. Микросхема также включает в себя два дополнительных ускорителя: ускоритель Stencil и Tensor (STX), разработанный Fraunhofer IIS, ITWM и ETH Zürich, и процессор переменной точности (VRP), созданный специалистами CEA LIST. Все ускорители подключены к высокоскоростной внутренней сети с помощью преобразователей, разработанных в EXTOLL.

Компания GlobalFoundries изготовила и корпусировала 143 экземпляра EPAC1.0 с использованием техпроцесса 22FDX, обеспечивающего низкое энергопотребление. На кристалле площадью 26,97 мм2 расположено 14 млн элементов компоновки (эквивалентно 93 млн ключей), включая 991 элемент памяти. Кристалл упакован в корпус FCBGA и рассчитан на таковую частоту 1 ГГц.

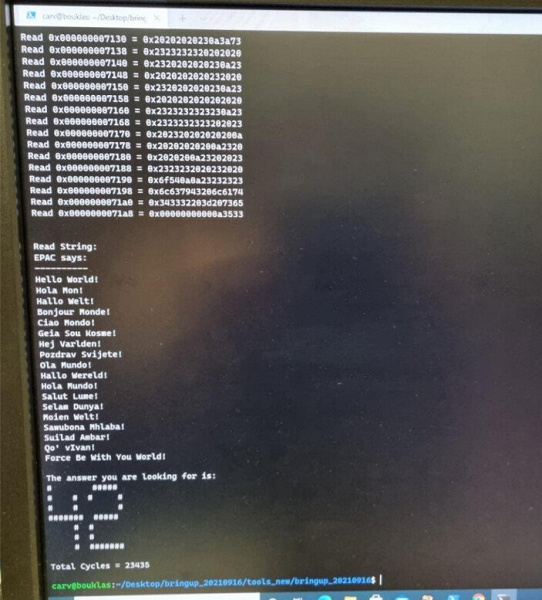

Процессор уже проверен в работе. На «голом железе» была выполнена первая программа, которая вывела традиционное сообщение «Hello World!» на разных языках.

EPI продолжит разработку, оптимизацию и проверку различных IP-ядер, которые впоследствии станут доступны производителям процессоров и ускорителей, а также представителям научных кругов, чтобы сделать возможным создание «глобально конкурентоспособных строительных блоков промышленного класса для суперкомпьютерных систем следующего поколения».